Analizator na Lcsoft CY7C68013A Mini Board

• tech • 2494 słowa • 12 minut czytania

Ta notatka została oznaczona jako wymagająca dopracowania: o brazki opt + transp.

Zawartość wpisu może ulec zmianie, zatem zapraszam do ponownych odwiedzin w niedalekiej przyszłości :)

Szukając jakiegoś szybkiego narzędzia mogącego zastąpić w działaniu prawdziwy analizator stanów logicznych, trafiłem na wiele modeli klonów, głównie chińskiego pochodzenia, ogólnie znanych producentów tego typu narzędzi, jak Saleaee czy USBee. Większość tych układów (klonów i oryginałów) bazuje na układach Cypressa EZ-USB FX2LP. Drążąc ten temat, znalazłem ciekawą płytkę deweloperską chińskiej firmy Lcsoft, będącej w rzeczywistości typową aplikacją układu CY7C68013A firmy Cypress. Sądząć po zawartości strony producenta, prezentującej układ, płytka ta powstała głównie w celu stworzenia taniego klona Saleae Logic.

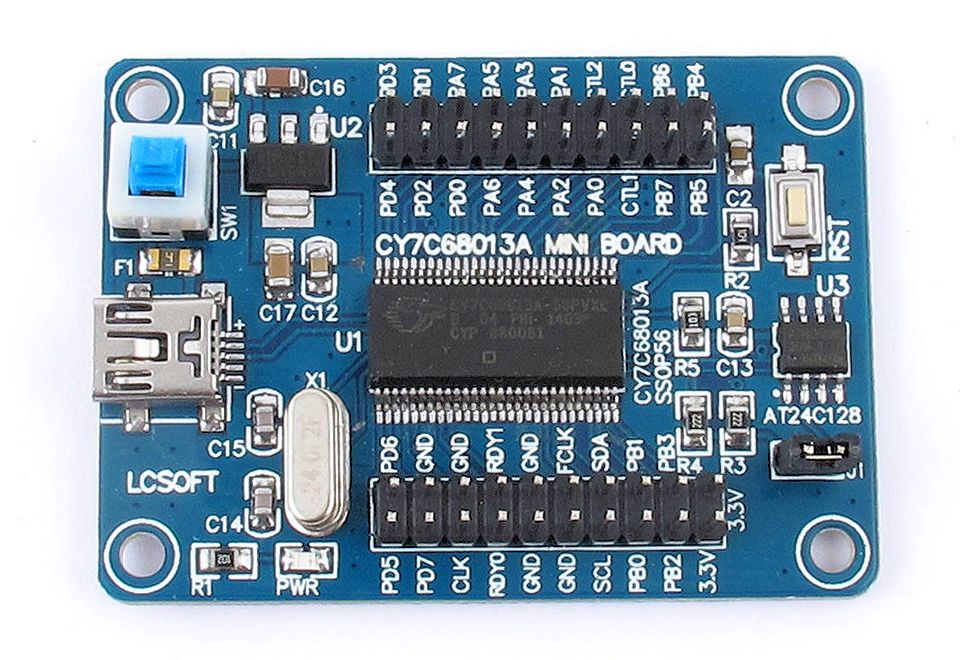

Lcsoft CY7C68013A Mini Board

Zdecydowałem się zdobyć omawianą płytkę zamiast dedykowanego, gotowego analizatora stanów logicznych, czy to w wersji oryginalnej (trochę drogo), czy podróbki/klona (bo wyjdzie na to samo). Głównie z dwóch powodów, wspominane produkty bazują na typowej aplikacji tego układu, a wersja deweloperska będzie dobrym sercem nie tylko dla analizatora logicznego, ale także może posłużyć do wielu innych ciekawych urządzeń lub narzędzi. Dobrym przykładem może być chociażby adapter USB-LPT, który również bardzo by mi się przydał. Szczególnie w czasach, gdy standardem jest USB, a szukanie portu szeregowego, nie wspominając o równoległym, w nowym sprzęcie skazane jest na porażkę.

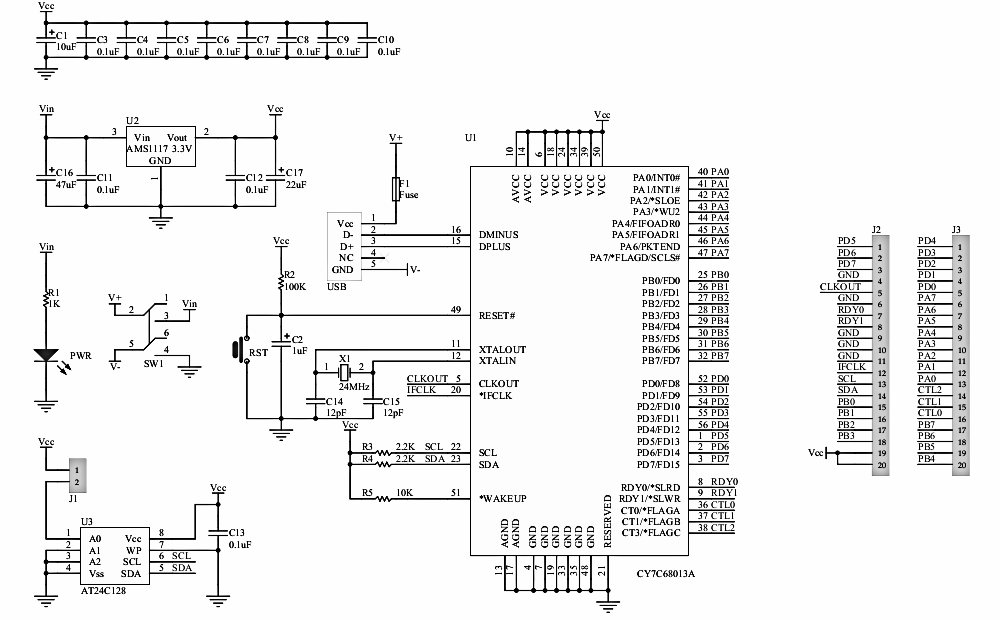

Jak już wspomniałem układ płytki prototypowej jest typową aplikacją kostki CY7C68013A wraz z wymaganymi elementami do jej prawidłowego funkcjonowania. Płytka zawiera ponadto pamięć EEPROM o pojemności 16KB (24LC128), w której, w pierwszych komórkach zapisane są numery VID i PID interfejsu USB, pozwalające na jednoznaczne identyfikowanie sprzętu. Oprócz tego można trzymać dowolne inne dane. Podłączeniem kostki pamięci można manipulować za pomocą zworki, dzięki czemu szybko można zmienić tryb pracy układu. Bez pamięci urządzenie przedstawi się jako zwykła płytka prototypowa Cypressa - “Cypress EZ-USB FX2LP No EEPROM(3.4.5.000)”. Wszystkie porty mikroprocesora wyprowadzone są na złącza (goldpiny), co jest standardem w tego typu układach. Także jest to idealna płytka do testowania i zabawy oraz szybkiego uruchomienia ciekawych rzeczy.

Schemat ideowy znaleziony w sieci, obrazujący omawiany układ, przedstawiono poniżej.

Chip CY7C68013A-56PVXC jest bazującym na ‘51 mikrokontrolerem USB, taktowany 48MHz, wspierający standard USB 2.0 z transmisją high-speed (480Mbps). Nie posiada własnej pamięci programu (typu flash), w której byłby przechowywany kod programu. Zamiast tego przy każdym uruchomieniu (bootowaniu), po przedstawieniu się w systemie, jest możliwość załadowania odpowiedniego oprogramowania wprost z komputera przez port USB. Robi to odpowiedni soft danego urządzenia.

Cena samej kostki różni się od sprzedawcy, w Polsce waha się w okolicach 50-75 złoty. U chińskich dostawców można znaleźć ceny zaczynające się od $4, a przy większej ilości trafi się jeszcze lepiej. Można również pokusić się o darmowe sample od producenta.

Za niewiele większą cenę można dostać gotową płytkę. Jest to dobre posuniecie, gdy zależy nam na wielofunkcyjnej płytce prototypowej. Dzięki temu otrzymujemy gotowy, zmontowany produkt, za przystępną cenę, dużo niższą niż samodzielne skompletowanie i wykonanie. A co najważniejsze, możemy od razu przejść do pracy. Ja za swój egzemplarz dałem $7, co jest prawie połowa tego za ile dostępny jest w kraju sam chip.

Dokładne informacje odnośnie układu płytki deweloperskiej można znaleźć na stronie producenta (link), a szczegółowe informacje o kostce Cypressa w dokumentacji (datasheet).

Dostęp do EEPROM z CyConsole

Jeśli dobrze kojarzę, a jestem tego prawie pewien, to w opisie była wzmianka, że standardowo będą w pamięci załadowane identyfikatory sprzętu odpowiadające urządzeniu Saleae Logic. Niestety trochę się zdziwiłem, bo po podłączeniu do laptopa, system wykrył urządzenie jako “USB-Blaster”. Nie pozostało nic innego jak zapisać w pamięci nowe wartości.

Dobrać się do pamięci EEPROM najprościej za pomocą konsoli CyConsole, którą można znaleźć w pakiecie Cypress Suite USB (wymaga logowania/konta w serwisie, ale można znaleźć w sieci bezpośrednie linki lub pliki - CySuiteUSB_3_4_7_B204.exe). Problemem mogą być sterowniki dla standardowej aplikacji Cypressa, bo nie ma podpisanych cyfrowo wersji dla Win7+. Problem ten można rozwiązać instalując je z innego źródła, jak chociażby przez USBee SX Drivers. Można również załatwić to przez Cypress Generic Driver, ponoć są one zawarte w CySuite, ale nie są one podpisane cyfrowo i wymagają trochę zabawy.

Vend_ax

Najbardziej popularnym, opisywanym w sieci oraz najszybszym sposobem komunikacji z EEPROM-em jest wykorzystanie programu Vend_ax. Ten firmware jest w rzeczywistości prostym przykładem demonstrującym jak zaimplementować specyficzne dla produktu (vendor) polecenia i komendy. Dołączony jest do pakietu EZ-USB FX2 Development Kit, bez problemu można także znaleźć w sieci bez potrzeby instalacji całego devkita.

Najbardziej intersujące z naszego punktu widzenia będą komendy typu load/save dla pamięci EEPROM, w programie odstępne są 2 ich wersje - 0xA2 dla małych pamięci (LC00) adresowany bajtem i 0xA9 dla wielkich (LC64) adresowanych słowem - 16 bitami. Jeśli w wyniku otrzymamy ciąg “CD CD CD...”, świadczy to o błędzie dostępu do pamięci EEPROM, może to oznaczać jakieś uszkodzenia albo próbę użycia nieodpowiedniej komendy adekwatnej do sposobu adresowania danej kostki.

Innym przydatnym poleceniem jest VR_GETI2C_TYPE (0xA5) pozwalające odczytać typ pamięci, a dokładniej rodzaj adresowania - 8 czy 16 bitów. Zwracająca odpowiednio 0x00 lub 0x01.

Całą listę możliwych poleceń dla Vendor_ax można znaleźć w źródłach:

VR_ANCHOR_DLD 0xa0 // handled by core

VR_EEPROM 0xa2 // loads (uploads) EEPROM

VR_RAM 0xa3 // loads (uploads) external ram

VR_SETI2CADDR 0xa4

VR_GETI2C_TYPE 0xa5 // 8 or 16 byte address

VR_GET_CHIP_REV 0xa6 // Rev A, B = 0, Rev C = 2 // NOTE: New TNG Rev

VR_TEST_MEM 0xa7 // runs mem test and returns result

VR_RENUM 0xa8 // renum

VR_DB_FX 0xa9 // Force use of double byte address EEPROM (for FX)

VR_I2C_100 0xaa // put the i2c bus in 100Khz mode

VR_I2C_400 0xab // put the i2c bus in 400Khz mode

VR_NOSDPAUTO 0xac // test code. does uploads using SUDPTR with manual length override

Cała filozofia zabawy ogranicza się do wyjęcia zworki J1 przed podłączeniem naszego układu do portu USB. W ten sposób płytka zostanie rozpoznana jako standardowa płytka Cypressa i będzie możliwy do niej dostęp z konsoli CyConsole. A gdy to uda się osiągnąć, z powrotem włączamy zewnętrzną pamięć przez zwarcie styków J1. Teraz możemy zacząć prawdziwą zabawę.

Ładujemy program Vend_ax.hex do chipa za pomoc opcji Download. Wpisujemy kod odpowiedniej komendy w polu Req, offset/adres komórki pamięci, której ma dotyczyć operacja - pole Value, ilość danych w Length, a także kierunek w Dir – IN to odczyt, OUT to zapis. Wysłanie żądania dokonujmy za pomocą przycisku Vend Req. Przy odczycie otrzymamy zrzut zawartości intersujących nas komórek pamięci. Przy zapisie w polu Hex Bytes wpisujemy dane które chcemy zapisać pod danym adresem.

Nie będę tutaj wnikał w szczegóły samego procederu. W sieci pełno różnej maści poradników i opisów, więc nie ma sensu dublować treści. Pomocny może być dokument przedstawiający tutorial do przykładu vend_ax. A graficzne treści można znaleźć na różnych stronach powiązanych z tematem uruchomienia lub sklonowania analizatorów logicznych na układach Cypressa (np. tutaj: USBee_SX/ZX_Hack).

Potrafiąc manipulować zawartością pamięci EEPROM, odczytałem zapisany identyfikator sprzętu. Wartość jaką otrzymałem, zgodnie z przypuszczeniami, odpowiadała urządzeniu “Usb-Blaster”. Niestety nie pamiętam dokładnie jakie wartości były zapisane w pamięci, gdzieś umknęły, ale VID/PID dla tego typu urządzenia to 0x9FB/0x6001.

Po załadowaniu wartości odpowiednich dla Saleae, czyli 0x0925 i 0x3881, które w pamięci powinny być zapiane poczynając od adresu zerowego, jako ciąg danych:

C0 25 09 81 38 00 00 00

Po resecie bez problemu urządzenie zostało rozpoznane jako “Saleae Logic”.

Magiczny pierwszy bajt 0xC0 jest instrukcją wymaganą przez CY7C68013A do odpowiedniego wystartowania, co dalej zostanie szerzej wyjaśnione.

Bootowanie, EEPROM i VID/PID

Warto zapoznać się bliżej z całym mechanizmem obsługi pamięci EEPROM, etapem bootowania i pobierania identyfikatorów VID/PID/DID przez układ CY7C68013A.

Numery VID i PID są unikalnymi identyfikatorami danego sprzętu, ich nadawaniem zajmuje się USB-IF. Wykupienie własnego VID-a obecnie kształtuje się na poziomie około $4000. To za ich pomocą system wie co zostało do niego podłączone. Układ CY7C68013A sam w sobie jest jakby uniwersalnym układem, któremu możemy przypisać dowolne identyfikatory dla budowanego układu lub urządzenia. Oczywiście jak wspomniałem, sam chipset posiada własne “standardowe” wartości tych identyfikatorów, aby można było z nim bez większego problemu “porozmawiać”. Ale domyślnie, w czasie bootowania następuje próba pobrania identyfikatora z dołączonej zewnętrznej pamięci EEPROM.

Układ EZ-USB FX2LP obsługuje dwa rodzaje pamięci EEPROM, o tym wspominałem wyżej, bez problemu radzi sobie z małymi jak i wielkimi - 1 i 2 bajtowo-adresowanymi kostkami. Aby to bezproblemowo działało musi być odpowiednio podłączone i adresowane. Chip na podstawie adresu urządzenia determinuje rodzaj podłączonej pamięci.

Zgodnie z dokumentacją (datasheet lub EZ-USB Technical Reference Manual) decydującym pinem adresu jest A0, który dla 8-bitowych adresów powinien znajdować się w stanie niskim, a dla 16-bitowych w stanie wysokim. Co implikuje dostępność 8-bitowych pamięci pod adresem 0xA0, a16-bitowych pod 0xA2 szyny I2C, jeśli chcemy wykorzystać pamięć w procesie bootowania. Po wykryciu typu podłączonej pamięci manual twierdzi, że EZ-USB zaraportuje wynik na liniach ID1 i ID0, ale osobiście tego nie sprawdzałem.

Chipset CY7C68013A obsługuje kilka trybów startowania: 3 tryby związane z pamięcią EEPROM oraz osobny tryb z zewnętrzną Flash, EPROM lub inną zawierającą firmware. Przy starcie wewnętrzne elementy sprawdzają dostępność poszczególnych elementów (pamięci), sposobu podłączenia i ich zawartości, na podstawie czego podejmują dalsze kroki.

Tryby związane z pamięcią EEPROM bazują na obecności (lub braku) połączenia z takową pamięcią w odpowiednim adresowaniu, o czym wyżej wspominałem.

Pierwszy z nich – standardowy, bez pamięci EEPROM lub z niepoprawnymi danymi bootowania, wtedy FX2LP przedstawi się jako standardowe urządzenie Cypressa, wykorzystując wewnętrzne zapisane identyfikatory VID/PID/DID - 0x04B4, 0x8613, 0xAxxx (gdzie xxx oznacza wersję chipu).

Kolejne 2 tryby używają pamięci EEPROM, w której pierwszy bajt determinuje jej zawartość i przeznaczenie. Gdy jest nim 0xC0, co mogliśmy wyżej już zobaczyć, oznacza, że kolejne 6 bajtów zawierają identyfikator urządzenia w kolejności VID PID DID, a na koniec 1 bajt z danymi konfigurującymi. Gdy 1-wszym bajtem będzie 0xC2 w czasie startowania zawartość pamięci EEPROM zostanie załadowana do pamięci RAM. Tutaj również kolejne 7 bajtów zawiera te same dane co w poprzednim trybie - identyfikatory, a za nimi odpowiednio sformatowane dane, mówiące co i gdzie załadować do pamięci operacyjnej.

Tryb ostatni z pamięcią Flash, EPROM lub inna zawierającą kod firmware, który zostanie wykonany po starcie szerzej opisuje manual do układu EZ-USB. W nim również znajdziemy dokładniejsze informacje na temat bootowania.

Klonowanie i testowanie

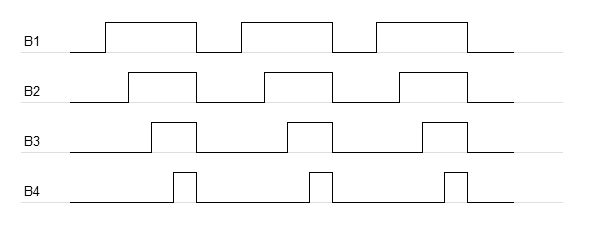

Po zabawach przyszedł czas na szybki test, aby upewnić się, że wszystko działa poprawnie. Wygrzebałem płytkę testową na atmedze, wrzucając prosty program generujący jakiś przebieg na dowolnym wyjściu. Kod w stylu:

DDRB = 0x0F;

while (1) {

PORTB = 0x01; // 00000001

_delay_ms(50);

PORTB = 0x03; // 00000011

_delay_ms(50);

PORTB = 0x07; // 00000111

_delay_ms(50);

PORTB = 0x0F; // 00001111

_delay_ms(50);

PORTB = 0x00; // 00000000

_delay_ms(100);

}

powinien wygenerować na wyjściu portu B przebieg podobny do:

Większość analizatorów logicznych jako wejścia wykorzystuje port B (dla pierwszych 8 kanałów) układu CY7C68013A, więc do nich należy podłączyć sondy pomiarowe. W przypadku wersji 16-kanałowych używany jest dodatkowo port D.

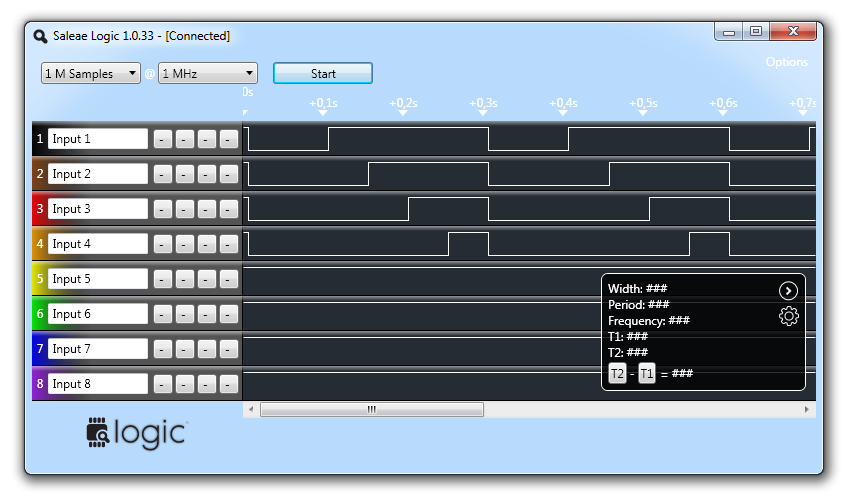

Saleae Logic

Analizator Saleae jest chyba najpopularniejszym urządzeniem tego typu, jest w miarę tani i szeroko stosowany przez rzesze elektroników na całym świecie. Po wrzuceniu w pamięć identyfikatorów tego urządzenia - 0x0925/0x3881/0x001B- płytka bez problemu pojawiła się w systemie jako Saleae Logic.

Po uruchomieniu aplikacji, przycisk do tej pory identyfikowany jako “Start simulation” zmienił swoją etykietę na “Start”. Po ustawieniu danych zrzutu/analizy i jego kliknięciu, zostają zbierane próbki. A po krótkim czasie wyrenderowane na ekranie.

Testowana wersja aplikacji Saleae to 1.0.33. Można ją znaleźć w otchłani sieci. Z aktualną wersją 1.1.15 płytka Lcsoft nie jest kompatybilna. Problemem jest prawdopodobnie zmiana oprogramowania firmware oraz aplikacji wykrywającą niekompatybilną pamięć EEPROM. W urządzeniach fabrycznych używane są małe pamięci adresowane bajtem, a nie słowem jak w układzie testowym.

Uruchomienie nowej wersji uświadczy nas wysypem aplikacji i błędem jaki możemy znaleźć w logach wygenerowanego raportu:

Error: LogicAnalyzerDevice::ReadEeprom failed after 3 tries.

Łatwo obejść ten problem zamieniając kostkę pamięci, w sieci pełno jest na ten temat informacji - na blogu spirala można trafić na ciekawy komentarz - So your Saleae clone isn’t working with the new software?. Ja niestety nie chcę bawić się lutownicą i iść w kierunku modyfikacji sprzętu, jak wszscy inni, ba nawet nie mam na stanie mniejszej kostki, aby to zrobić. Jest to problem software-owy, a nie hardwer-owy i w ten sposób będę starał się go obejść. Więcej informacji o tym problemie i efektach może za kilka dni się pojawi na blogu. Całkiem ciekawa zabawa może z tego wyniknąć.

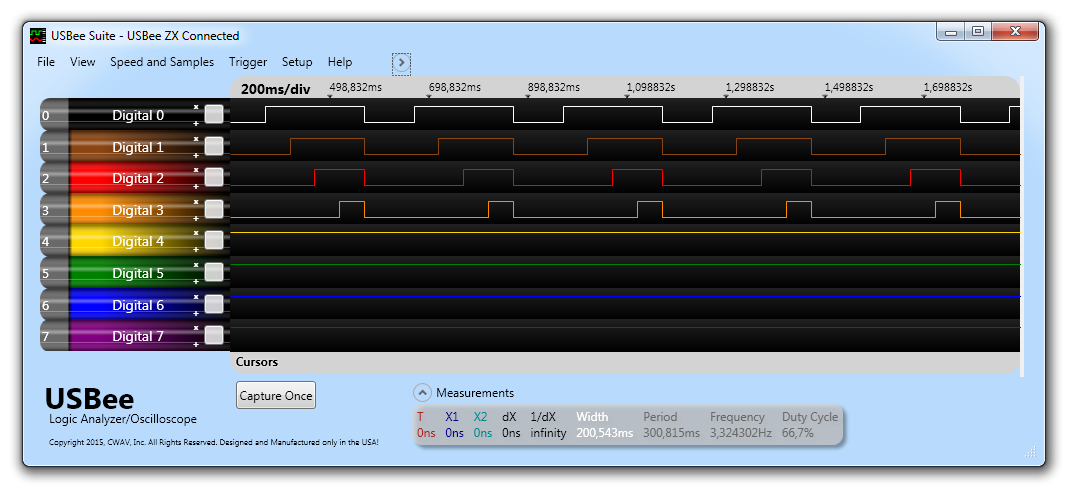

USBee ZX/SX

Po zainstalowaniu pakietu USBee Suite i wrzuceniu odpowiednich identyfikatorów VID i PID do pamięci, wszystko bez problemów ruszyło. Wersja SX – 0x08A9/0x0009 i ZX - 0x08A9/0x0005.

Nowsze, rozbudowane wersje posiadają również wejścia analogowe i możliwość badania takich sygnałów. Niestety wymagają one już nieco bardziej rozbudowanego sprzętu niż sam chipset Cypressa.

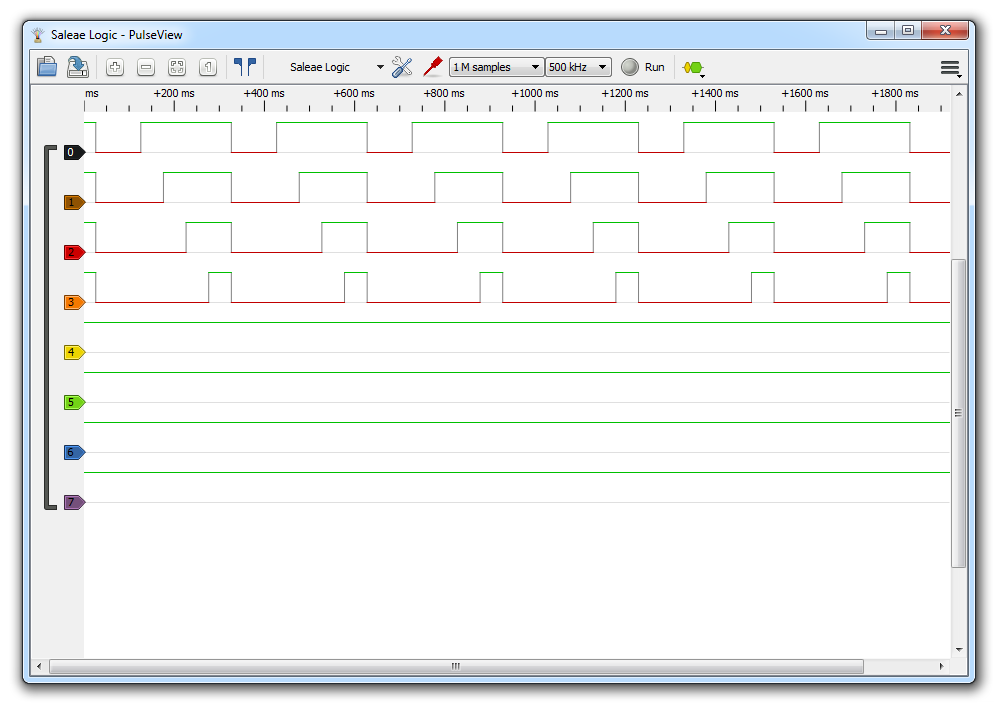

sigrok PulseView

Alternatywą dla komercyjnych rozwiązań jest ciekawy, open-sourcowy projekt singrok. Jest to implementacja własnego, multi-platformowego i otwartego firmware - Fx2lafw i software - dla analizatora logicznego. Działa na dowolnym urządzeniu z CY7C68013A. Pełną listę obsługiwanego hardware można znaleźć na stronach projektu.

Moja płytka identyfikowana jako Saleae bez problemu ruszyła z singrokowym GUI - PulseView.

Więcej informacji można znaleźć na stronach projektu.

Co dalej?

Większość analizatorów, czy to komercyjnych, czy też otwartych konstrukcji, posiada o wiele więcej ciekawych i przydanych opcji. Najbardziej popularna jest analiza wyników i ich przystepna prezentacja. Prawie każde oprogramowanie do tego służące potrafi analizować, wykrywać ogólnie znane protokoły i magistrale oraz ładnie prezentować dane. Są to niewątpliwe plusy, bardzo ułatwiające prace, szczególnie przy reversowaniu różnych nieznanych układów.

Niektóre układy prócz typowo cyfrowych wejść maja także wejścia analogowe, co wraz z zawartym w układzie przetwornikiem ADC w znacznym stopniu poszerza możliwości układu. Zdarzają się nawet opcje umożliwiające nie tylko odczyt, ale także generowanie własnych sygnałów na wyjściach. Ciekawą, autorską implementację generatora PWM działającego na sprzęcie Saleae można znaleźć tutaj: Saleae Logic PWM generator.

Wykorzystanie gołej płytki testowej Cypressa w roli analizatora logicznego nie jest dobrym pomysłem. Warto pomyśleć o odpowiednim zabezpieczeniu portów wejściowych służących za wejścia pomiarowe. Układ będzie służył w głównej mierze do badania nieznanych nam układów i przebiegów, a w czasie eksperymentów łatwo przez pomyłkę, czy nieświadomie podpiąć sondę w nieodpowiednie miejsce. Dobrze przemyślane i wykonane układy buforujące, czy izolujące (np. optoizolacja) zabezpieczą chipset oraz port USB przed ewentualnym uszkodzeniem. Osobiście sam planuję takowe zabezpieczania wykonać, mam nadzieje, ze nastąpi to wcześniej niż później. Obecnie traktuję płytkę testową Lcsoftu z modułem Cypressa w roli analizatora jako tymczasową prowizorkę.

W zasobach Internetu można znaleźć naprawdę wiele ciekawych informacji na temat analizatorów logicznych, tych komercyjnych przedstawionych wyżej oraz innych własnych autorskich konstrukcji.

Na naszym rodzimym podwórku jedną z lepszych i popularnych konstrukcji opartych na chipsecie Cypressa jest układ manekinena - Uniwersalna Płytka Analizatora Logicznego. Również na elektrodzie można trafić na ciekawe konstrukcje i dyskusje poruszające ten temat - Analizator logiczny na CY7C68013A.

Czasami, w nagłych sytuacjach, w roli analizatora można wykorzystać port równoległy komputera - Analizator stanów logicznych na LPT lub dowolny mikrokontroler. Układ taki można na prędce zbudować, czego przykładem może być Scanalogic oparty na atmedze lub inna wersja z wbudowanym własnym wyświetlaczem - 4-input mini Logic Analyzer.

Dla znających Cycrylicę lub lubiących zabawę z translatorem, na rosyjskim forum kazus.ru można znaleźć ciekawy wątek poruszający tematykę klonowania, własnych konstrukcji i rozwiązań dotyczących analizatorów logicznych - Осваиваем USBee. Również na easyelectronics.ru można znaleźć bliższe spojrzenie na chińskie klony - И снова про китайские анализаторы (доработка клона USBee DX).

Ja tymczasem wracam do wspomnianych i obiecanych działań mających na celu znalezienie programowego rozwiązania problemu z niekompatybilną pamięcią EEPROM w nowych wersjach Saleae Logic. Liczę, że za kilka dni będę mógł przedstawić jakieś ciekawe wnioski i uwagi z przeprowadzonych eksperymentów.

Komentarze (0)